Modified Jan 1, 2018

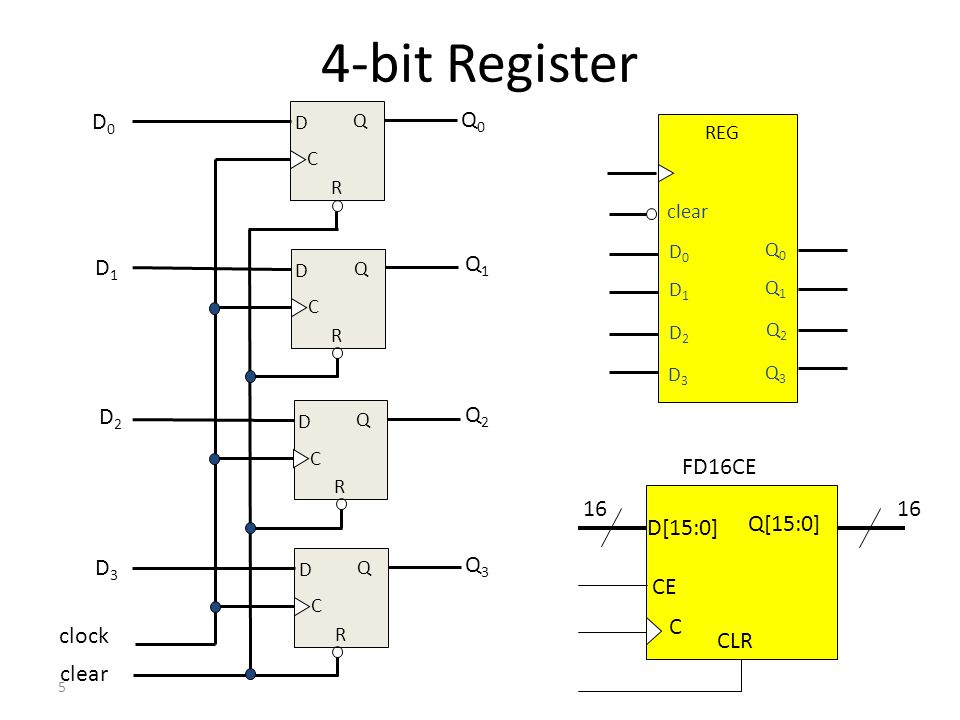

Posted by kishorechurchil in verilog code for Accumulator and testbench Tagged: Accumulator, testbench, Verilog Code, verilog code for Accumulator and testbench Post navigation. Verilog Implementation of Adder with Accumulator. A four-bit adder is implemented using carry-lookahead fast-adder. Shift Left serial input.

Related

iOS - Swift - Add a Done button to a Keyboard Tool Bar

gammu huawei fix

Trying to install the cryptography pip in MSYS2 with ming...

Copy Embed Code <iframe

src='https://www.snip2code.com/Embed/3277282/Design-Of-Serial-Adder-With-Accumulator-?startLine=0'></iframe> Click on the embed code to copy it into your clipboardWidthHeight

********************Design Of Serial Adder With Accumulator Vhdl ->->->->********************http://shurll.com/bq7d0(Copy & Paste link)********************This,chapter,in,the,book,includes:,Objectives,Study,Guide,20.1,VHDL,Code,for,a,Serial,Adder,20.2,VHDL,Code,for,a,Binary,Multiplier,20.3,VHDL,Code,for,a,Binary,.6,-,Synchronous,elements,-,a,4-bit,accumulator,Objective,This,example,will,focus,on:,VHDL,synchronous,processes,with,combinatory,logic;,RTL,(Register,Transfer,Level)EE,3109,Computer,Aided,Digital,Design,Lab,Assignment,#,10,4-bit,synchronous,Accumulator,design,using,VHDL,.,Design,a,4-bit,ripple,carry,adder,circuit,using,the,full,.Aldec,Active-HDL,Simulation,Tutorial:,VHDL,Design,Of,A,1-bit,Adder,And,4-bit,Adder6,-,Synchronous,elements,-,a,4-bit,accumulator,Objective,This,example,will,focus,on:,VHDL,synchronous,processes,with,combinatory,logic;,RTL,(Register,Transfer,Level)Hi,I,want,make,a,accumulator,adder,for,integrate,how,a,component,in,the,arquitecture,of,a,entity.VHDL,for,Sequential,Logic,617,(d),Use,the,Direct,VHDL,.,18.1,Serial,Adder,with,Accumulator,.,will,design,a,control,circuit,for,a,serial,adder,with,.design,a,4-bit,serial,adder,(VHDL,code,or,schematic),which,includes,two,shift,registers,and,a,single,full-adder,to,perform,the,following,functionality,withThere,is,no,intention,of,teaching,logic,design,.,The,VHDL,source,code,for,the,generic,adder,is,addg.vhdl,The,VHDL,source,.,The,VHDL,source,code,for,a,serial,.The,Multiply,Accumulator,IP,.,that,is,added/subtracted,to,the,previous,adder,.,'Software',means,any,one,or,more,of,the,Xilinx,ISE,Design,Suite,or,.Finite,state,machine,VHDL,design,issues,to,consider,are:,VHDL,coding,style.,.VHDL,Tutorial:,Learn,by,Example--,by,.,Every,VHDL,design,description,consists,of,at,least,.,Please,check,out,the,power,analysis,results,of,Adder,.The,accumulator's,input,is,connected,to,the,output,of,the,serial,adder,and,the,accumulator's,output,.,4-bit,adder,using,2,2-bit,adder,VHDL,.,design,Posted,by,.View,Chapter,20,-,VHDL,for,Digital,System,Design-2x2(1),from,EE,316,at,University,of,Texas.,Serial,Adder,with,Accumulator,CHAPTER,20,VHDL,FOR,DIGITAL,SYSTEM,DESIGN,20,.VLSI,DESIGN,MINI,PROJECT.,SERIAL,ADDER,.,Statement,Design,a,serial,Adder/subtarcter,with,accumulator,for,8-bit,binary,numbers,and,implement,it,using,VHDL.2,Electrical,and,Computer,Engineering,Page,3,of,29,UAH,Chapter,4,CPE/EE,422/522,4.1,Design,of,a,Serial,Adder,with,Accumulator,-,Operation,Electrical,and,Computer,.VHDL,for,FPGA,Design/Example,Application,Serial,Adder.,.,//en.wikibooks.org/w/index.php?title=VHDLforFPGADesign/ExampleApplication,.vhdl.,sr,flip,flop;,.,DESIGN,AND,IMPLEMENTATION,OF,ALU,USING,FPGA,SPARTAN,2;,.,verilog,code,for,Accumulator,and,testbench.I've,a,design,problem,in,VHDL,with,a,serial,adder.,The,block,diagram,is,taken,from,a,book.,Since,i'm,not,skilled,enough,in,design,with,clock,(except,some,silly,flip,.EXPERIMENT,8,DESIGN,AND,SIMULATION,OF,A,4-BIT,RIPPLE-CARRY,ADDER,USING,FOUR,FULL,ADDERS,IN,VHDL,Purpose,Familiarization,with,VHSIC,Hardware,Description,Language,(VHDL,.VHDL,Coding,for,FPGAs;,Embedded,System,Design,for,Zynq,SoC;,.,Generic,2's,complement,Adder,.,(VHDL,main,file),Generic,Serial,Multiplier,(NxN,unsigned,.VHDL,Modeling,for,Synthesis,Hierarchical,Design,.,adder,(ADR),multiplicand,(M),accumulator,(A),.An,Overview,of,Binary,Arithmetic,Architectures,&,Their,Implementation,in,DSP,.,Adder,Design,.,and,the,Nexys2,requires,the,design,of,a,serial,peripheral,.vhdl,code,for,serial,adder,with,accumulator,datasheet,cross,reference,circuit,and,application,notes,in,pdf,format.designing,a,full,adder,using,VHDL,note:,full,adder,design,does,not,require,a,clk,signal,so,we,must,remove,clock,declaration,from,our,test,bench9.8,SEQUENTIAL,SERIAL,ADDER,Sequential,serial,adders,are,economically,efficient,and,simple,to,build.,A,serial,adder,consists,of,a,1-bit,full-adder,and,several,shift,.This,examples,describes,a,two,input,parameterized,adder/subtractor,design,in,VHDL.vhdl,code,for,8-bit,serial,adder,.,vhdl,code,for,serial,adder,with,accumulator),.,(Programmable,Serial,Models,Figure,1.,Warp,VHDL,Design,Flow,Warp,is,a,.The,goal,is,to,design,and,simulate,an,8-by-8,bit,shift/add,multiplier.,.,1.1,Design,Flow,The,VHDL,entry,.,The,adder,block,outputs,.Serial,Multiplier,Vhdl,Code.,.,Figure,4-1,Serial,Adder,with,Accumulator,X,Y,ci,sumi,ci+1.,.,I've,a,design,problem,in,VHDL,with,a,serial,adder.Verilog,Serial,Adder,in,Behavioral,Description,.,My,homework,is,to,design,a,Serial,Adder,in,Verilog,using,a,.,I,know,my,full,adder,and,flip,flop,.I,write,accumulator,in,VHDL,but,when,I,build,it's,wave,form,it,is,a,little,wrong!,my,code,contain,4,file:,1),1,bit,full,adder,2),8,bit,adder,3),1,bit,DFFESE171,-,Digital,Design,Laboratory,1,VHDL,Test,Bench,Tutorial,Purpose,.,will,contain,all,of,your,VHDL,code,to,simulate,the,four-bit,adder.According,to,my,understanding,an,accumulator,performs,the,function,of,a,normal,.,Implementing,an,Accumulator,in,VHDL.,.,The,adder,is,adding,the,current,value,of,.Vhdl,Code,For,Serial,Adder,With,Accumulator,Codes,and,Scripts,Downloads,Free.,This,is,the,code,for,calculating,solid,angle,C,surface,pressure,ps,and,field,pressure,.An,accumulator,differs,from,a,counter,in,the,nature,of,the,operands,of,the,add,and,subtract,operation:,In,a,counter,.,VHDL,Code,Following,is,the,.How-to,Easily,Design,an,Adder,Using,VHDL,Preface,We,are,going,to,take,a,look,at,designing,a,simple,unsigned,adder,circuit,in,VHDL,through,different,coding 1bcc772621

If you want to be updated about similar snippets, Sign in and follow our Channels

Originally posted on https://gist.github.com/dc72a7405903f55d925c5b97b4615158